# LAN9500/LAN9500i LAN9500A/LAN9500Ai

## USB 2.0 to 10/100 Ethernet Controller

### PRODUCT FEATURES

**Data Brief**

### **Highlights**

- Single Chip Hi-Speed USB 2.0 to 10/100 Ethernet Controller

- Integrated 10/100 Ethernet MAC with Full-Duplex Support

- Integrated 10/100 Ethernet PHY with HP Auto-MDIX support

- Integrated USB 2.0 Hi-Speed Device Controller

- Integrated USB 2.0 Hi-Speed PHY

- Implements Reduced Power Operating Modes

- ±8kV HBM ESD protection (component level)

- ±8kV contact-discharge, ±15kV air discharge

ESD protection per IEC61000-4-2

#### **Target Applications**

- Embedded Systems

- Set-Top Boxes

- PVR's

- CE Devices

- Networked Printers

- USB Port Replicators

- Standalone USB to Ethernet Dongles

- Test Instrumentation

- Industrial

### **Key Features**

- USB Device Controller

- Fully compliant with Hi-Speed Universal Serial Bus Specification Revision 2.0

- Supports HS (480 Mbps) and FS (12 Mbps) modes

- Four endpoints supported

- Supports vendor specific commands

- Integrated USB 2.0 PHY

- Remote wakeup supported

- High-Performance 10/100 Ethernet Controller

- Fully compliant with IEEE802.3/802.3u

- Integrated Ethernet MAC and PHY

- 10BASE-T and 100BASE-TX support

- Full- and half-duplex support

- Full- and half-duplex flow control

- Preamble generation and removal

- $^{1}$  = LAN9500A/LAN9500Ai only

- Automatic 32-bit CRC generation and checking

- Automatic payload padding and pad removal

- Loop-back modes

- TCP/UDP/IP/ICMP checksum offload support

- Flexible address filtering modes

- One 48-bit perfect address

- 64 hash-filtered multicast addresses

- Pass all multicast

- Promiscuous mode

- Inverse filtering

- Pass all incoming with status report

- Wakeup packet support

- Integrated Ethernet PHY

- Auto-negotiation

- Automatic polarity detection and correction

- HP Auto-MDIX support

- Link status change wake-up detection

- Support for 3 status LEDs

- External MII and Turbo MII support HomePNA™ and HomePlug® PHY

- Power and I/Os

- Various low power modes

- NetDetach feature increases battery life <sup>1</sup>

- Supports PCI-like PME wake <sup>1</sup>

- 11 GPIOs

- Supports bus-powered and self-powered operation

- Integrated power-on reset circuit

- Single external 3.3v I/O supply

- Internal core regulator

- Miscellaneous Features

- EEPROM Controller

- Supports custom operation without EEPROM <sup>1</sup>

- IEEE 1149.1 (JTAG) Boundary Scan

- Requires single 25 MHz crystal

- Software

- Windows XP/Vista Driver

- Linux Driver

- Win CE Driver

- MAC OS Driver

- EEPROM Utility

- Packaging

- 56-pin QFN (8x8 mm) Lead-Free RoHS Compliant

- Environmental

- Commercial Temperature Range (0°C to +70°C)

- Industrial Temperature Range (-40°C to +85°C)

SMSC LAN950x Family Revision 1.1 (04-18-13)

#### **Order Numbers:**

LAN9500-ABZJ (Tray) for 56-pin, QFN lead-free RoHS compliant package (0 to +70°C temp range)

LAN9500-ABZJ-TR (Tape & Reel) for 56-pin, QFN lead-free RoHS compliant package (0 to +70°C temp range)

LAN9500i-ABZJ (Tray) for 56-pin, QFN lead-free RoHS compliant package (-40 to +85°C temp range)

LAN9500i-ABZJ-TR (Tape & Reel) for 56-pin, QFN lead-free RoHS compliant package (-40 to +85°C temp range)

LAN9500A-ABZJ (Tray) for 56-pin, QFN lead-free RoHS compliant package (0 to +70°C temp range)

LAN9500A-ABZJ-TR (Tape & Reel) for 56-pin, QFN lead-free RoHS compliant package (0 to +85°C temp range)

LAN9500Ai-ABZJ (Tray) for 56-pin, QFN lead-free RoHS compliant package (-40 to +85°C temp range)

LAN9500Ai-ABZJ-TR (Tape & Reel) for 56-pin, QFN lead-free RoHS compliant package (-40 to +85°C temp range)

This product meets the halogen maximum concentration values per IEC61249-2-21 For RoHS compliance and environmental information, please visit www.smsc.com/rohs

Copyright © 2013 SMSC or its subsidiaries. All rights reserved.

Circuit diagrams and other information relating to SMSC products are included as a means of illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the described semiconductor devices any licenses under any patent rights or other intellectual property rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated version of SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or errors known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of this document or other SMSC literature, as well as the Terms of Sale Agreement, may be obtained by visiting SMSC's website at http://www.smsc.com. SMSC is a registered trademark of Standard Microsystems Corporation ("SMSC"). Product names and company names are the trademarks of their respective holders.

The Microchip name and logo, and the Microchip logo are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE. IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

## **Overview**

The LAN950x is a high performance Hi-Speed USB 2.0 to 10/100 Ethernet controller. With applications ranging from embedded systems, set-top boxes, and PVR's, to USB port replicators, USB to Ethernet dongles, and test instrumentation, the device is a high performance and cost competitive USB to Ethernet connectivity solution.

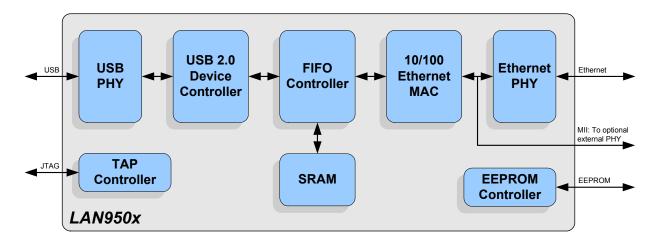

The LAN950x contains an integrated 10/100 Ethernet PHY, USB PHY, Hi-Speed USB 2.0 device controller, 10/100 Ethernet MAC, TAP controller, EEPROM controller, and a FIFO controller with a total of 30 KB of internal packet buffering.

The internal USB 2.0 device controller and USB PHY are compliant with the USB 2.0 Hi-Speed standard. The device implements Control, Interrupt, Bulk-in, and Bulk-out USB Endpoints.

The Ethernet controller supports auto-negotiation, auto-polarity correction, HP Auto-MDIX, and is compliant with the IEEE 802.3 and IEEE 802.3u standards. An external MII interface provides support for an external Fast Ethernet PHY, HomePNA, and HomePlug functionality.

Multiple power management features are provided, including various low power modes and "Magic Packet", "Wake On LAN", and "Link Status Change" wake events. These wake events can be programmed to initiate a USB remote wakeup.

An internal EEPROM controller exists to load various USB configuration information and the device MAC address. The integrated IEEE 1149.1 compliant TAP controller provides boundary scan via JTAG.

Figure 1 System Diagram

# **Package Outline**

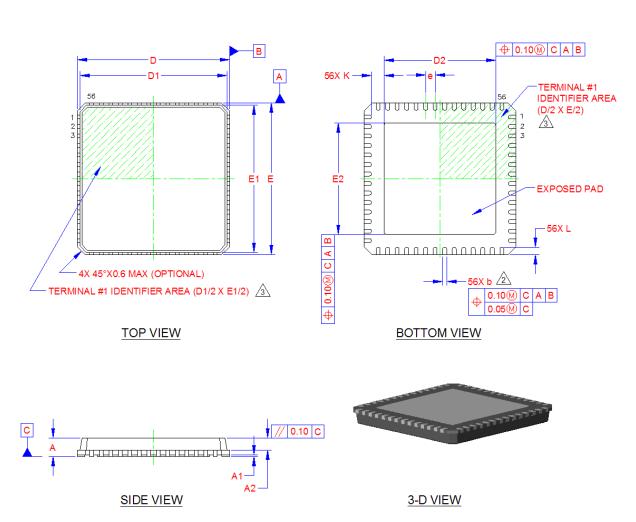

Figure 2 LAN950x 56-QFN Package

Table 1 LAN950x 56-QFN Dimensions

|       | MIN  | NOMINAL  | MAX  | REMARKS                     |  |

|-------|------|----------|------|-----------------------------|--|

| Α     | 0.70 | 0.85     | 1.00 | Overall Package Height      |  |

| A1    | 0.00 | 0.02     | 0.05 | Standoff                    |  |

| A2    | -    | -        | 0.90 | Mold Cap Thickness          |  |

| D/E   | 7.85 | 8.00     | 8.15 | X/Y Body Size               |  |

| D1/E1 | 7.55 | 7.75     | 7.95 | X/Y Mold Cap Size           |  |

| D2/E2 | 5.80 | 5.90     | 6.00 | X/Y Exposed Pad Size        |  |

| L     | 0.30 | 0.40     | 0.50 | Terminal Length             |  |

| b     | 0.18 | 0.25     | 0.30 | Terminal Width              |  |

| K     | 0.55 | -        | -    | Center Pad to Pin Clearance |  |

| е     |      | 0.50 BSC |      | Terminal Pitch              |  |

### Notes:

- 1. All dimensions are in millimeters unless otherwise noted.

- 2. Position tolerance of each terminal and exposed pad is +/- 0.05 mm at maximum material condition. Dimension "b" applies to plated terminals and is measured between 0.15 and 0.30 mm from the terminal tip.

- 3. The pin 1 identifier may vary, but is always located within the zone indicated.

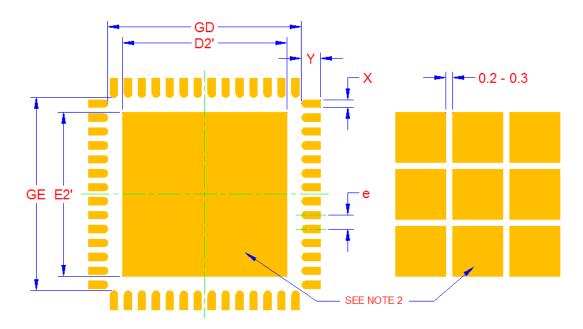

| LAND PATTERN DIMENSIONS |      |      |      |  |  |  |  |

|-------------------------|------|------|------|--|--|--|--|

| SYMBOL                  | MIN  | NOM  | MAX  |  |  |  |  |

| GD/GE                   | 6.93 | -    | 7.05 |  |  |  |  |

| D2'/E2'                 | -    | 5.90 | 5.90 |  |  |  |  |

| X                       | -    | 0.28 | 0.28 |  |  |  |  |

| Y                       | -    | 0.69 | 0.69 |  |  |  |  |

| е                       | 0.50 |      |      |  |  |  |  |

### NOTES:

- THE USER MAY MODIFY THE PCB LAND PATTERN DESIGN AND DIMENSIONS BASED ON THEIR EXPERIENCE AND/OR PROCESS CAPABILITY

- 2. EXPOSED SOLDERABLE COPPER AREA OF THE CENTER PAD CAN BE EITHER SOLID OR SEGMENTED

- 3. MAXIMUM THERMAL AND ELECTRICAL PACKAGE PERFORMANCE IS ACHIEVED WHEN AN ARRAY OF SOLID VIAS IS INCORPORATED IN THE CENTER LAND PATTERN

## PCB LAND PATTERN

Figure 3 LAN950x 56-QFN Recommended PCB Land Pattern

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# Microchip:

<u>LAN9500A-ABZJ LAN9500-ABZJ-TR LAN9500AI-ABZJ-TR LAN9500I-ABZJ-TR LAN9500I-ABZJ LAN9500A-ABZJ-TR LAN9500AI-ABZJ LAN9500-ABZJ LAN9500-AB</u>